2.3. Isolated DC/DC conversion stage¶

The isolated DC/DC converter stage allow the user to design and simulate a converter which includes a galvanic isolation provided by a HF transformer.

2.3.1. Getting started¶

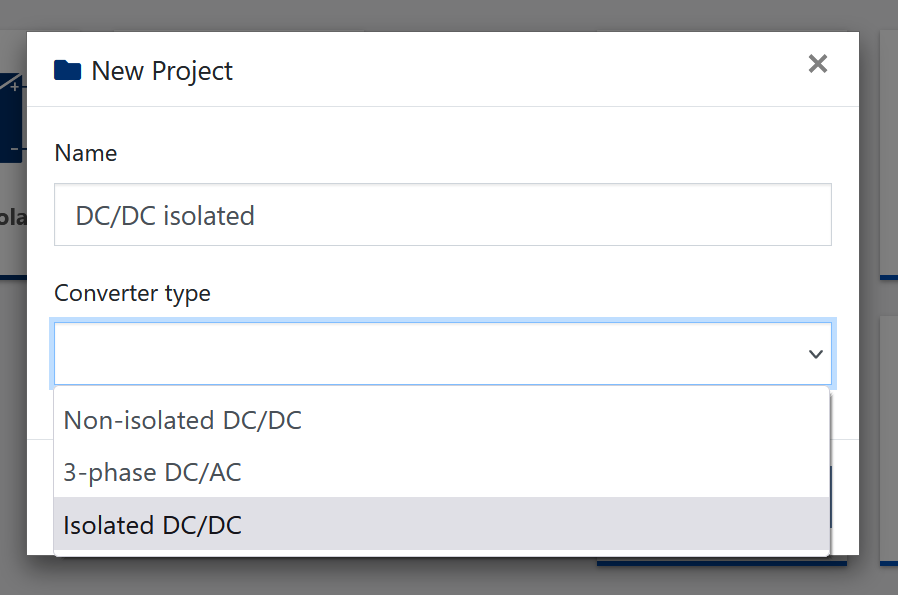

To create a new project click the ➕ button, enter a name for the new project, select your converter type and confirm. Your browser will automatically load the newly created project’s page.

2.3.2. Converter definition¶

The isolated DC/DC works with two bridges and an isolated tank that includes a high frequency transformer and other elements such as inductors and capacitors. The side on the left of the transformer is named “Primary side” and the right “Secondary side”. The power is filtered by two DC filters on both sides. The two bridges are controlled by a single switching controller in open loop.

The isolated DC/DC converter is composed of 8 subsystems as described in the next figure:

The Switching controller for both bridges named “Switching Controller”

The primary bridge named “Macrocell Primary”

The secondary bridge “Macrocell Secondary”

The Isolated tank between the two bridges

The cooling system for the Macrocell Primary

The cooling system for the Macrocell Secondary

The DC filter in the primary side named “HV Filter Primary”

The DC filter in the secondary side named “HV Filter Secondary”

2.3.2.1. Conventions and operating points¶

An isolated DC/DC converter performs bidirectional power conversion between two DC buses.

Since this conversion stage is current-bidirectional, there is no fixed ‘input’ or ‘output’ side.

The reference power is defined on the Secondary side, hence total converter efficiency is computed by PowerForge as such:

if \(P_{Secondary}>0\) then \(η = \dfrac { |P_{Secondary}| }{ |P_{Secondary}| + P_{loss} }\)

if \(P_{Secondary}<0\) then \(η = \dfrac { |P_{Secondary}| - P_{loss} }{ |P_{Secondary}|}\)

2.3.3. Source modeling¶

2.3.3.1. Ideal DC sources¶

When using this operating point definition, the conversion stage’s Secondary and Primary interfaces are both modeled as connected to an ideal DC source. The natures of these sources depend on the order of the corresponding filters.

At the interfaces:

Odd order filters will be connected to a current source (only 1st order filter available for the moment)

Even order filters will be connected to a voltage source.

2.3.4. Subsystems¶

2.3.4.1. Switching controller¶

The switching controller subsystem automatically find the control parameter in order to meet the target operating point. There is 3 different switching controller mode available:

2.3.4.1.1. Dual Active Bridge (DAB) Phase Shift Mode¶

In this mode, the two bridges are commanded and the power transfer is controlled by the phase shift between the two bridges. The phase-shift value is automatically determined to match the target Secondary Power.

Input parameters

Switching Frequency (fsw):

Apparent switching frequency of the bridge on both sides

Duty cycle primary/secondary:

Apparent Duty cycle of the primary/secondary bridge on the AC side defined between 0 and 0.5. For half a period, the duty cycle defines the ratio of time at +VDC (or -VDC) and the time at 0V.

At DutyCycle = 0.5, the output voltage is a pure square between +VDC and -VDC.

At DutyCycle = 0.25, the output voltage is 0V half the time, a quarter at +VDC and a quarter at -VDC.

At DutyCycle = 0, the output voltage is zero.

Decoder Type primary/secondary:

In order to have a zero voltage on the AC side, different switch configurations are possible depending on the type of macrocell. Depending on the decoder type, the switch control changes to make the output 0V. It impacts the switching loss and conduction loss of the switches. The usage of “Top/Bot” configuration is suggested as all switches will have the same loss. Other configurations can be interesting depending on the operation mode: “Top” means the zero voltage is performed with both top switches (T1 & T3) conducting, and “Bot” means the zero voltage is performed with both bottom switches (T2 & T4) conducting.

T1 |

T2 |

T3 |

T4 |

AC Voltage |

1 |

0 |

0 |

1 |

+VDC |

1 |

0 |

1 |

0 |

0 (Top) |

0 |

1 |

1 |

0 |

-VDC |

0 |

1 |

0 |

1 |

0 (Bot) |

Other decoder available

T1 |

T2 |

T3 |

T4 |

AC Voltage |

1 |

0 |

0 |

1 |

+VDC |

1 |

0 |

1 |

0 |

0 (Top) |

0 |

1 |

1 |

0 |

-VDC |

1 |

0 |

1 |

0 |

0 (Top) |

T1 |

T2 |

T3 |

T4 |

AC Voltage |

1 |

0 |

0 |

1 |

+VDC |

0 |

1 |

0 |

1 |

0 (Bot) |

0 |

1 |

1 |

0 |

-VDC |

0 |

1 |

0 |

1 |

0 (Bot) |

T1 |

T2 |

T3 |

T4 |

AC Voltage |

1 |

0 |

0 |

1 |

+VDC |

0 |

1 |

0 |

1 |

0 (Bot) |

0 |

1 |

1 |

0 |

-VDC |

1 |

0 |

1 |

0 |

0 (Top) |

Output parameters

Phase Shift:

The phase shift between the two bridges output voltage (AC voltage) allows the power flow control. This parameter is automatically determined based on the target operating point and the waveforms obtained with PowerForge frequential MNA solver.

2.3.4.1.2. Dual Active Bridge (DAB) Triangular Mode¶

In this mode, the control is similar to the phase shift mode as the two bridges are commanded. The particularity of the DAB triangular mode is a control scheme that ensure Zero Current Switching of some devices. The duty cycles are changing depending on the phase shift with the equations below, and deducted from the reference 1 2:

It is recommended to use the (top/bot) decoder in the case.

Input parameters

Switching frequency: The same as explained in section Dual Active Bridge (DAB) Phase Shift Mode

Decoder type: The same as explained in section Dual Active Bridge (DAB) Phase Shift Mode

Output parameters

Phase Shift: The same as explained in section Dual Active Bridge (DAB) Phase Shift Mode

Duty cycle primary: The same as explained in section Dual Active Bridge (DAB) Phase Shift Mode

Duty cycle secondary: The same as explained in section Dual Active Bridge (DAB) Phase Shift Mode

2.3.4.1.3. Single Active Bridge (SAB) mode¶

The Single Active Brige (SAB) mode, is a control scheme that considered only one commanded bridge and a bridge in passive rectification. The synchronous rectification on the passive bridge is possible if compatible device are selected (MOSFET, GaN device)

The active bridge changes depending on the power sign. If the power is positive, the primary bridge is active, otherwise , it is the secondary bridge.

This kind of control method is designed to be used with resonant isolated tank (LLC, CLLC, CLLLC)

Input parameters

Duty cycle: This parameter represent the active bridge duty cycle.

Decoder type: The decoder principle is the same as explained in section Dual Active Bridge (DAB) Phase Shift Mode

Output parameters

R_load:

With this switching controller selection, the isolated tank modelling is modified. Indeed, the passive bridge is modeled as a resistor, in a similar way as the first harmonic approximation (FAH) usually done to analyse the isolated tank gain curve. However, as the active bridge generated non-sine waveform, an iterative process allow the right Rload calculation to ensure the right energy dissipation by the resistor and the target operating point. The used Rload value is displayed in the switching controller section of a design result.

Switching frequency:

Apparent switching frequency of the active bridge. The value is automatically determined through an iterative process at the same time as the Rload. The switching frequency is represented in regard to the isolated tank gain curve available in the switching controller section of a design result.

2.3.4.2. Isolated tank¶

The isolated tank represents the passive components used to make the galvanic isolation between the two bridges. As a consequence, it always includes a transformer and at least an inductor to interface the two voltage sources that are the primary and secondary DC bus. It can also include capacitor banks and an additional inductor.

Available variants

L-type

It includes a transformer and an inductor. In this variant, the user can select transformer models that do not include a parasitic magnetizing inductance. This variant needs to be used with DAB switching controller

LLC-type

It includes a transformer, an inductor and a capacitor.

CLLC-type

It includes a transformer, an inductor and a capacitor in the primary and in the secondary sides.

CLLLC-type

It includes a transformer, an inductor in the primary and in the secondary sides, and a capacitor in the primary and in the secondary sides.

2.3.4.3. Macrocell¶

2.3.4.3.1. Topology and semiconductor devices¶

As of today, one topology is available: the H-bridge (full bridge). The semiconductor devices in the topology are imposed to be homogeneous: the 4 devices of the topology are the same references. All technologies of semiconductor devices available in the library can be used.

2.3.4.3.2. Semiconductor device losses¶

The procedure to handle the two switching types (hard and soft switching) is as follow: at first, the waveforms are generated with the PowerForge fast frequential MNA 3 solver with perfect switch model. Then, the switching instants, the type of switching, and the switched voltage and current are estimated based on the waveforms. The algorithm to differentiate the soft-switching event and le hard switching events is presented in the next paragraph. The switching losses are estimated based on the waveforms by using lookup tables of switching energies stored into a database, one for hard-switching and the other for soft-switching. Finally, all the losses are summed for each switching instant. The loss estimation algorithm also includes an electro-thermal convergence loop discussed here 4. The switching energies lookup tables depend on 3 parameters: The switched current (Icell), the high voltage seen by the switch (Vds or Vce) and the junction temperature (Tj).

The switching event finder concept is based on the switching cell concept, illustrated in the figure below. The Low Side switch (LS) and the High Side switch (HS) are commanded with the signal Scell as presented. For example, if Icell>0 and Scell present a rising edge (Scell↑), the HS switch will have a controlled turn-on and the LS switch a uncontrolled turn-off producing turn-on loss (Eon) and recorvery loss on the HS diode (Err). If Icell>0 and Scell present a falling edge (Scell↓), the HS switch will have a controlled turn-off and the LS switch an uncontrolled turn-on. The turn off will produce turn-off loss (Eoff) and the uncontrolled turn-on of a switch caused by of a diode is supposed lossless.The four cases are summarised in the table below.

In a case of the usual rotation of controlled turn-on/turn-off, the hard-switching energies lookup table is used to estimate the loss. However, in a case of more than one consecutive controlled turn-off without controlled turn-on, the cell considered to be in a ZVS condition, and the soft-switching data are chosen.

The main advantage of this method lays in the flexibility in switching energy data handling and fast simulation capabilities.

Scell↑ |

Scell↓ |

|

Icell > 0 |

HS turn-on (HS Eon + LS Err) |

HS turn-off (HS Eoff or HS Esw soft) |

Icell <0 |

LS turn-off (LS Eon + HS Err) |

LS turn-on (HS Eoff or HS Esw soft) |

2.3.4.3.3. Switching energies estimation based on modified double pulse simulation¶

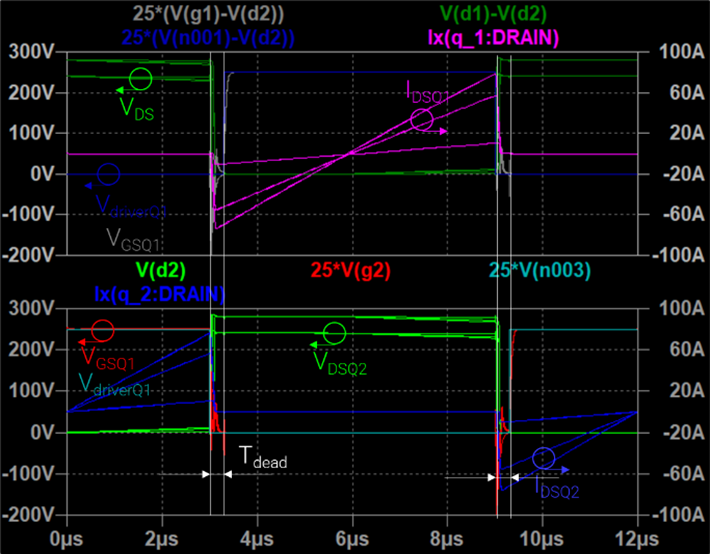

The switching energies data is usually extracted from manufacturer datasheets or from measurement results. However, when the data is not available a modified double pulse simulations is performed by the PowerForge team to estimate the energies (both for hard-switching and soft-switching) The modified double pulse test is for now only available for MOSFET devices. The double pulse simulation is perfomed based on a LTSPICE MOSFET model as presented in the figures below and presented in 4.

The LTSPICE model parameters are obtained from different sources:

the transconductance or diode parameters are extracted from the datasheet,

the parasitic capacitances values are lookup table digitalized form the same datasheet,

the parasitic common source inductance which is known to be a key parameter for switching losses estimation 5, 6

is estimated based on the package used 7 8 9.

It can be noted that this virtual test bench can be used with LTSPICE model given by semiconductor device manufacturers, but convergence issues can happen.

For soft-switching energy measurement, a modified double pulse is used as explained in 10, 11. The Device Under Test (DUT) is the LS device named Q2. The waveforms of the measurement setup are displayed in the figure below for multiple Vds bias, switched current and temperature.

At the start, Q2 is ON and Q1 OFF, the current will rise to the target switched current at the turn-off time for Q2. During device switch-off, the energy is measured. After a dead time, the Q1 device is controlled turned-on; if the dead time is well calibrated, the switching energy will be zero. Because of the polarity change across the inductance, the current decreases and becomes negative as Q1 is ON, simulating a ZVS. When the current becomes equal to the target negative switched current, Q1 is turned-off and Q2 (the DUT) naturally turned-on at that time, the energy released by the component is measured, mainly due to the Coss discharge. If the inductor current is insufficient to fully discharge the output capacitor leading to incomplete soft-switching 12, the measurement period extends to the controlled turn-on of the DUT after the dead time period. The switching time is also measured to give further information for dead time.

In summary, the switching energy loss is measured during the turn-off and the turn-on. However, as the turn-on is uncontrolled the energy stored in Coss is recuperated by the system (E<0). Eswsoft is then lower than Eoff if the soft-switching is attained. As a consequence, the incomplete soft-switching energy is also estimated.

2.3.5. Citations¶

- 1(1,2)

Nikolaus Schibli, “Symmetrical Multilevel converters with two quadrant DC-DC feeding,” Ecole Polytechnique fédérale de Lausanne (EPFL), 2000.

- 2

Krismer, “Modeling and optimization of bidirectional dual active bridge DC-DC converter topologies,” Doctoral Thesis, ETH Zurich, 2010. doi: 10.3929/ethz-a-006395373.

- 3

Fontes et al., “Fast Solver to Get Steady-State Waveforms for Power Converter Design,” in PCIM Europe 2018; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Jun. 2018, pp. 1–7.

- 4(1,2)

Fontes, F. Boige, A. Morentin, G. Delamare, T. Meynard, and N. Videau, “Semiconductor loss estimation in an innovative global power converter designer,” in PCIM Europe digital days 2020; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Jul. 2020, pp. 1–7.

- 5

Reusch, “Impact of Parasitics on Performance,” p. 5, 2020.

- 6

Bo Yang and J. Zhang, “Effect and utilization of common source inductance in synchronous rectification,” in Twentieth Annual IEEE Applied Power Electronics Conference and Exposition, 2005. APEC 2005., Austin, TX, USA, 2005, vol. 3, pp. 1407–1411. doi: 10.1109/APEC.2005.1453213.

- 7

“Features and Benefits of 650 V CoolMOSTM C6 / E6.” Infineon application note.

- 8

“650 V CoolMOSTM C7 Gold in TOLL package.” Infineon Product Brief.

- 9

Zhang, “Choosing The Right Power MOSFET Package.” International Rectifier application note.

- 10

Lefebvre, F. Costa, and F. Miserey, “Influence of the gate internal impedance on losses in a power MOS transistor switching at a high frequency in the ZVS mode,” IEEE Trans. Power Electron., vol. 17, no. 1, Art. no. 1, Jan. 2002, doi: 10.1109/63.988667.

- 11

Rothmund, D. Bortis, and J. W. Kolar, “Accurate Transient Calorimetric Measurement of Soft-Switching Losses of 10-kV SiC mosfets and Diodes,” IEEE Trans. Power Electron., vol. 33, no. 6, Art. no. 6, Jun. 2018, doi: 10.1109/TPEL.2017.2729892.

- 12

Kasper, R. Burkat, F. Deboy, and J. Kolar, “ZVS of Power MOSFETs Revisited,” IEEE Trans. Power Electron., pp. 1–1, 2016, doi: 10.1109/TPEL.2016.2574998.