3.1. Macrocell subsystem¶

The ‘macrocell’ in PowerForge is a generalization of the basic (2-level) switching cell found at the heart of a switching power converter. Unlike a 2-level converter which has only one pair of switches per phase leg, multilevel topologies and/or interleaved paralleling can have many more. However, they are collectively driven by a single switching controller to perform the same basic function (chopping a DC voltage into the desired waveform) as a basic switching cell - hence macrocell.

The macrocell subsystem is therefore connected to filters on both sides:

Contents

3.1.1. Different types of macrocell¶

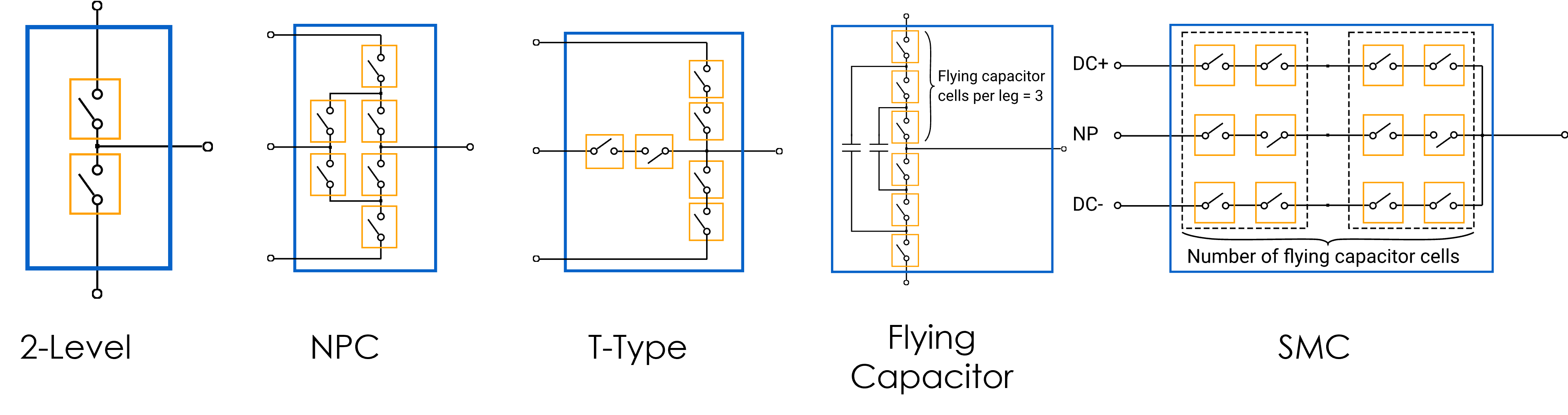

The different multilevel topologies supported by PowerForge are shown in the figure below:

All these topologies can be used for DC/AC applications, but only the 2-level and flying capacitor topologies can be used in DC/DC applications.

3.1.2. Models and assumptions¶

3.1.2.1. Physical construction¶

A macrocell is in practice built using packaged semiconductor switches from one of PowerForge’s libraries:

discretes or single-switch modules (only 1 switch per package)

leg modules (containing usually 1 to 3 pairs of identical switches arranged as phase legs)

NPC modules (containing usually 1 to 3 NPC legs)

T-type modules (containing usually 1 to 3 T-type legs)

Discrete switches or leg modules can be direct-paralleled to handle larger currents according to the parameter nswitch(par). NPC and T-type modules cannot be direct-paralleled this way.

The parallel assembly of nswitch(par) switches is treated as a single larger switch:

currents are equally shared and switching happens at the same instant

junction temperatures are equal

only one switch symbol is drawn in the circuit schematic, with total currents and losses displayed

nswitch(par) should not be confused with the number of parallel interleaved cells ncell(par) available in some topologies. The figure below shows two examples of two interleaved switching cells (ncell(par) = 2) where each switch position is also assembled from two direct-paralleled switches (nswitch(par) = 2):

the left example shows the use of direct-paralleled discrete switches

the right example shows the use of direct-paralleled leg modules

3.1.2.2. Homogeneous, Heterogeneous and module variants¶

Topologies are constituted with transistors + diodes commonly referred as switches. The number of switches depends on the number of parallelized switches, number of interleaved legs, number of phases and topology used as explained in detail above. The switch reference that can be used in the topologies differs depending on the topology variant used.

Three main variant available are:

Homogeneous: all the switches used in the topologies are made with the same reference from the discrete and leg module library. All the topologies supported in GT-PowerForge include this variant.

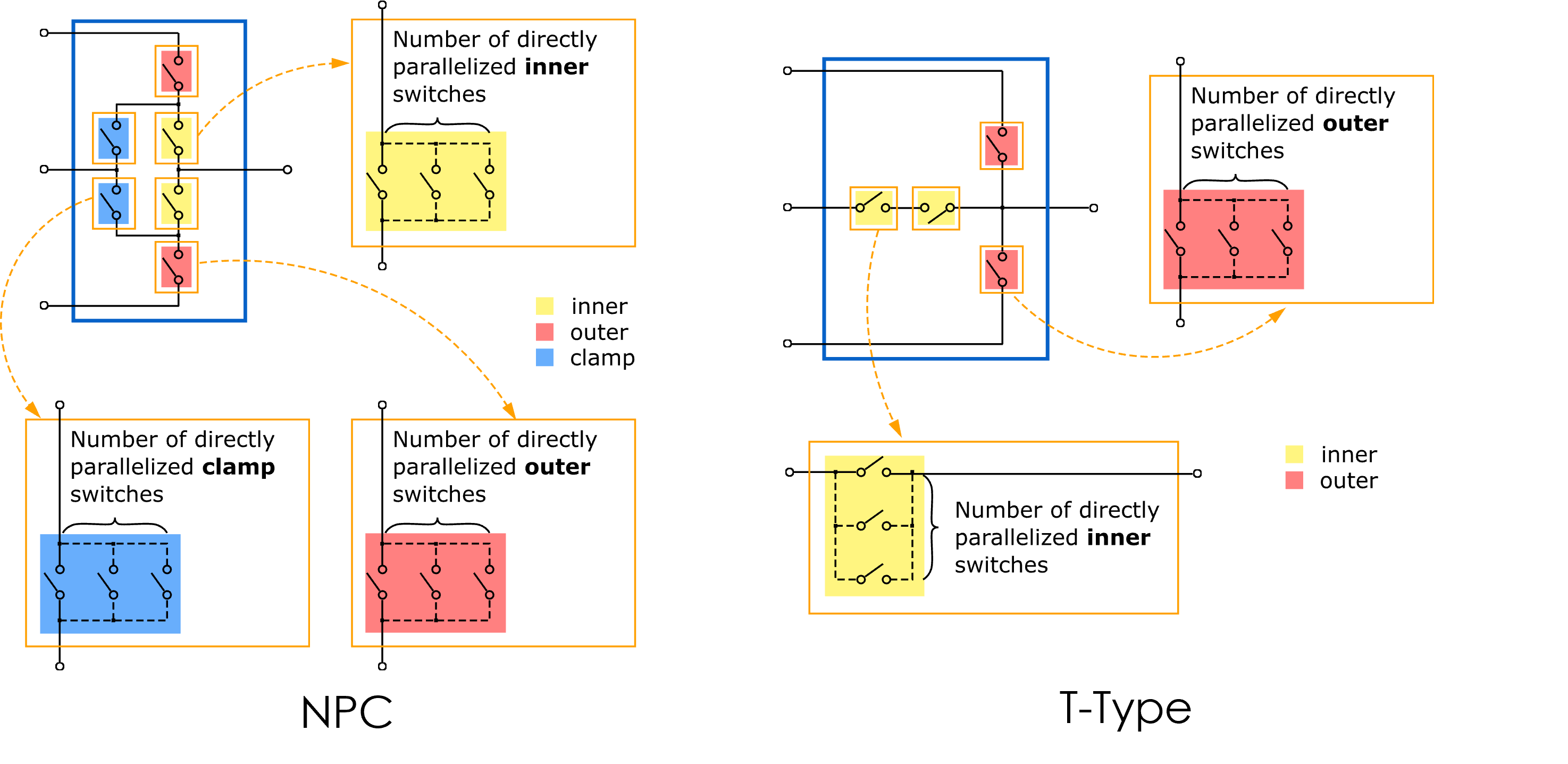

Heterogeneous: the switch reference used in the topology can be different depending on the switch position.

The switches references are from discrete and leg module library. The NPC and T-type topologies support this variant. It should be noted that using this variant, the recovery losses (Err) might be overestimated or underestimated. Indeed, the recovery losses highly depends on the switching speed of the opposing device and are usually measured with an homogeneous leg. By using an heterogeneous cell, the switching speed of the opposed switch might be different from the measurement as a different reference is used, thus adding some uncertainties to the recovery losses estimation value. In the NPC topology, Inner, Outer and Clamp switches can be different. In the T-type topology, the Inner and Outer switches can be different.

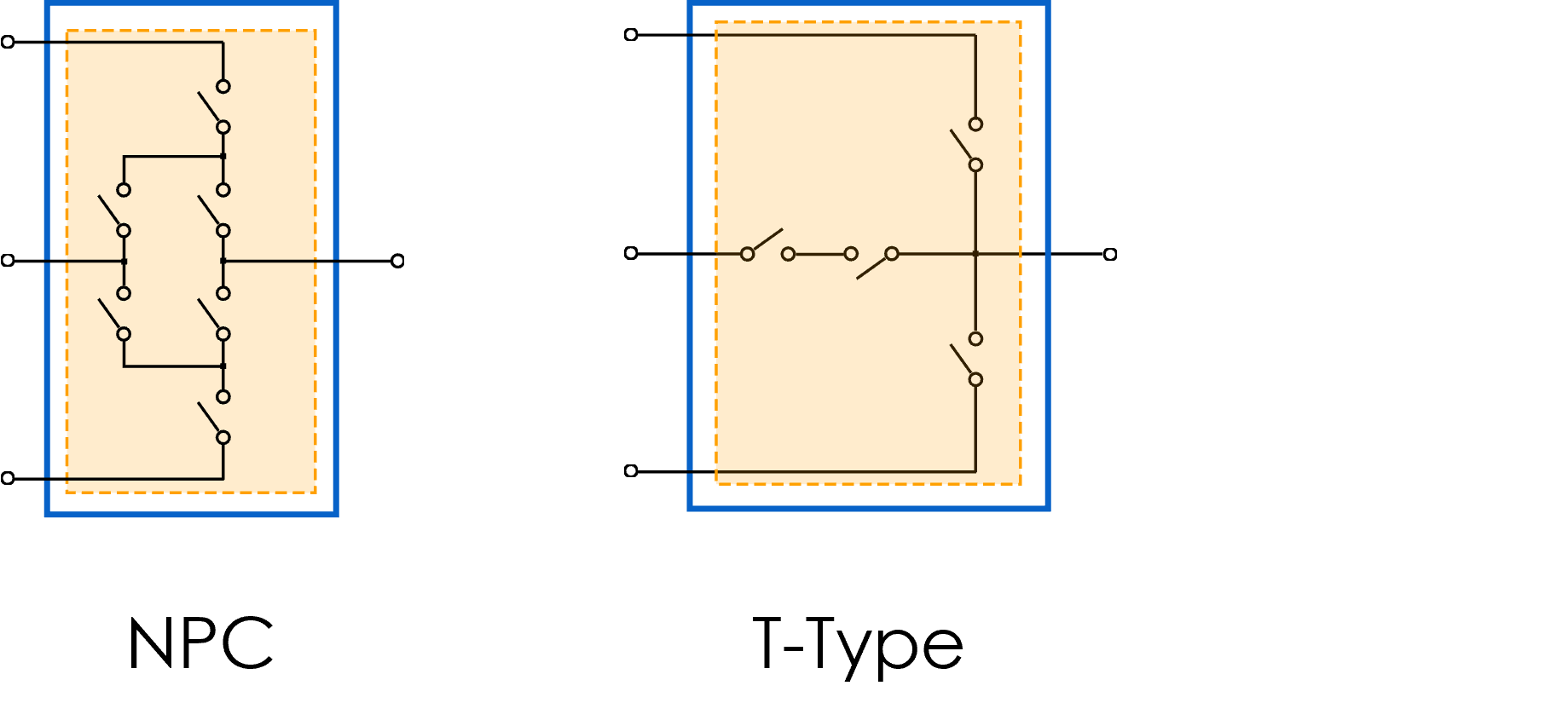

Module: this variant is only supported for NPC and T-type. All the switches in a leg are described in T-Type module or NPC modules libraries.

3.1.2.3. Electrical model¶

PowerForge assumes switches to be ideal when computing the converter’s switching waveforms. Conduction and switching loss are only computed a posteriori from these waveforms. This approach, typical in circuit simulators dedicated to power electronics, is very satisfactory as long as losses do not exceed a few percent of transferred power.

Knowing the ideal switches’ control pattern allows to model the macrocell as such:

on the low voltage side, ncell(par) square voltage sources with amplitude \(V_{HV} / n_{cell(fc)}\) and frequency \(n_{cell(fc)} \cdot f_{sw}\),

on the high voltage side, a square current source for each stacked switching cell.

The ripple of VHV is assumed small enough to not be taken into account neither when determining the chopped voltage applied to the low voltage side circuit nor when determining switching losses (the same assumption applies to flying capacitors’ voltages, for topologies using them).

The ripple of ILV is not taken into account when determining the chopped current applied to the high voltage side circuit.

3.1.2.4. Loss model¶

PowerForge assumes the thermal time constant to be much greater than the steady-state electrical waveforms’ periods:

power loss values are steady-state averages,

thermal equilibrium junction temperature of each chip is assumed to be constant.

Switch conduction voltage drops and switching energies are stored in PowerForge’s library as lookup tables, which are linearly interpolated when computing losses corresponding to the steady-state waveforms.

In the following formulas, \(i(t)\) is the overall instantaneous current in the switch or parallel assembly of nswitch(par) switches.

3.1.2.4.1. Conduction loss¶

Control deadtimes between turn-off of a switch and turn-on of its complementary switch are assumed to be negligible with regards to conduction loss. The conduction loss dissipated in each switch chip is the average product of \(V_{drop} \cdot i\) over the steady-state current waveform period \(T\):

When only one of the switch’s conduction mechanisms (spontaneous reverse or forward controlled) is used, the voltage drop is linearly interpolated from the corresponding \(V_{drop}=f(i, T_j)\) library lookup table.

When conducting reverse current, synchronous rectification is used if the transistor’s technology allows it (e.g. MOSFET). This means the transistor’s gate is assumed to be driven high, so that its controlled conduction mechanism (e.g. channel) can contribute to reverse current conduction. In this case, the reverse current may split between controlled and spontaneous reverse conduction mechanisms (e.g. diode and channel) in a ratio that depends on total reverse current and each junction temperature. PowerForge handles this and will therefore compute conduction loss due to each conduction mechanism’s current share.

3.1.2.4.2. Switching loss¶

The switching loss dissipated in each switch is the sum of turn-off, turn-on and reverse-recovery energies for each switching event occuring in the steady-state current waveform period, divided by this period’s duration \(T\):

These switching energies are linearly interpolated from the corresponding library lookup tables:

\(E_{off}=f(i_{off}, V_{switched}, T_j)\)

\(E_{on}=f(i_{on}, V_{switched}, T_j)\)

\(E_{rr}=f(i_{on}, V_{switched}, T_j)\)

Although negligible, the presence of a short deadtime is assumed present in the case of synchronous rectification: a switch will always be conducting the full reverse current via its diode before the complementary switch turns on, so that reverse-recovery losses always happen (despite the reverse current being mostly carried by the controlled conduction mechanism for the purposes of conduction loss computation).

3.1.2.5. Thermal model¶

Packaged switches have a junction-to-case thermal resistance (two, in the case of separate transistor and diode chips) specified from the heat-generating semiconductor structure inside the chip to the mounting / thermal dissipation surface on the outside of the package. This surface (usually a tab for discrete packages and a baseplate for modules) can be electrically isolated or not from the switches inside.

The macrocell’s thermal model also takes into account the case-to-heatsink thermal resistance due to the thermal interface product used for mounting the switches to the cooling device (and adding electrical isolation if necessary). Such products include thermal greases, elastomer pads and phase change materials.

PowerForge assumes no thermal coupling between switches upstream of the cooling device (whether these switches are in the same module or not).

3.1.2.6. \(R_G\) dependant model¶

Switch data can be provided as function of the gate resistance. Especially, the switching energies and the dv/dt curves. If the user wants to evaluate the impact of \(R_G\) in a design, the Discrete / leg modules (Rg Dependant) variant need to be used. In this variant, The Reference list only display the switch that contains switching energies and the dv/dt curves dependant of \(R_G\).

The \(R_{G,ON}\) and \(R_{G,OFF}\) are defined by the user through the use of a multiplication factor defined as \(k_{Rg,on}\) and \(k_{Rg,off}\) based on the default \(R_{G}\) values. If the \(R_{G}\) is equal to zero, the \(R_{G}\) is equal to \(k_{Rg}\). To summarise:

\[\begin{split}& if \quad R_{G,ON,Default} \neq 0 \\

& \quad R_{G,ON} = k_{Rg,on} \cdot R_{G,ON,Default} \\

& else \\

& \quad R_{G,ON} = k_{Rg,on} \\\end{split}\]

|

\[\begin{split}& if \quad R_{G,OFF,Default} \neq 0 \\

& \quad R_{G,OFF} = k_{Rg,off} \cdot R_{G,OFF,Default} \\

& else \\

& \quad R_{G,OFF} = k_{Rg,off} \\\end{split}\]

|

3.1.2.6.1. Switching loss¶

The \(R_{G,ON}\) and \(R_{G,OFF}\) values are used to interpolate/extrapolate the switching energies lookup tables stored in the library as described in switching loss.

If a \(R_G\) dependant reference is used with the default Discrete / leg modules variant, the default \(R_{G,ON}\) and \(R_{G,OFF}\) are used to interpolate the switching loss lookup tables.

3.1.2.6.2. Switching speed (dv/dt)¶

The \(R_{G,ON}\) and \(R_{G,OFF}\) values are used to interpolate/extrapolate the dv/dt(on) and dv/dt(off) lookup tables stored in the library as described in switching loss.

The individual switch maximum switching speed can be seen in the tab “data” in the macrocell section in the design detail view (design dashboard)

The maximum switchin speed of all the switches in the macrocell is also used to estimate the voltage peak at the machine terminal if the LCR dv/dt filter model is used